近来,GlobalFoundries宣布将会推进7nm FinFET工艺,引发了行业对工艺节点、光刻等技术的探讨。本文是来自SemiEngineering 2014年的一篇报道,带领大家了解7nm工艺及以后的半导体业界的发展方向。

随着尖端芯片制造商将其产品推向16nm、14nm、10nm甚至7nm制程,相关供应商也在更新其技术蓝图。现在华为海思、三星和高通等芯片制造商正在媒体上披露其10nm芯片的出货规划,Global Foundries,、Intel、三星和TSMC也正在循序渐进的推进其工艺制程,Global Foundries甚至还在日前公布了其7nm计划。

但随着工艺节点的推进,硅材料本身的局限逐渐显现,加上ASML的EUV光刻机迟迟未能交付,业界对于摩尔定律在7nm、5nm和之后的制程是否有效发表了不同的见解。从我们的角度看来,10nm节点工艺的实现是没有什么问题的(如今已经成为事实,10nm量产在即),但到了7nm和之后的制程,则面临更大的挑战。7nm是否能顺利量产,5nm是否还有可能,3nm是否只存在于想象之中,(这句话读起来不通)。

但有一点可以肯定,那就是到了10nm之后,我们不能像在以往节点一样,通过简单地缩小栅极宽度来推进工艺制程。往7nm的迁移势必需要昂贵的全新晶体管架构、沟道材料和内部连接。同时还需要全新的Fab工具和材料。但就我们观察,这些目前都不够成熟。

从技术的角度看来,我们可以生产7nm或5nm芯片。但设计和生产这些制程的芯片,则需要极强的资金和能力。另外,在有多重选择的当下,如何选择正确的技术也是实现这些制程的关键。

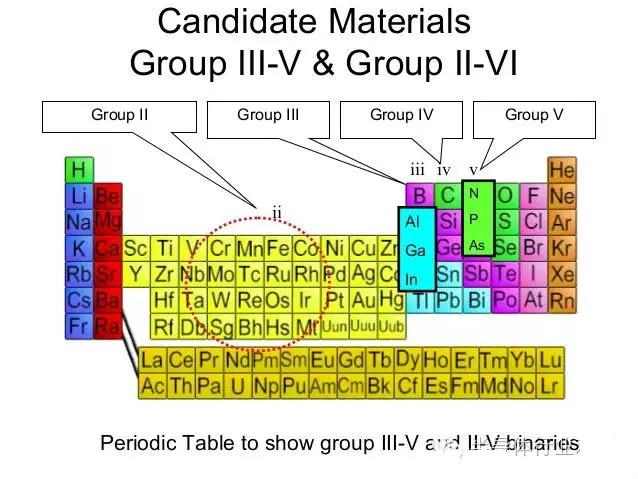

从之前的路线图看来,在7nm制程,最有希望的晶体管候选者就是高电子迁移率的III-V族FinFET,而之后的5nm则会迎来下一代的晶体管。

但近来这些现状都已经改变了,根据IMEC的一些报告显示,虽然III-V族 inFET可能会应用在7nm上,但他们认为最终会在5nm的时候普及(这句话不对劲,是不是普及的是下一代结构的晶体管?)。所以根据IMEC的观点,下一代的晶体管可能会在7nm上就出现。

其实在7nm的时候,有三种晶体管可以选择,分别是环绕栅极场效应晶体管、量子阱FinFET和SOI FinFET。根据IMEC的报告,环绕栅极场效应晶体管是最好的选择,但现在来宣告胜利者还是为时过早。同样,锗或者III-V族材料都应该是7nm时沟道的首选材料之一(首选,又是之一?)。

其实一直以来,业界都在寻找一个性价比能接受的方案。但现在芯片制造商们似乎正在加速推进其所选择的技术,并将其推向市场,以取得竞争优势。

从IMEC的报告中我们可以发现,在其CMOS计划中,其研发和合作伙伴包括了Global Foundries, Intel,三星和TSMC等。IMEC会和他们一起缩窄选择范围,并做出最终的选择。

基于IMEC及IMEC合作伙伴路线图,产业有可能在2018年进入7nm时代(从今年来看,可能要推迟)。不必惊奇,他们都希望能解决芯片尺寸继续缩小的问题,或许这将真的是摩尔定律的终点。问题是不管未来7nm能否达到,或是会有一些推迟,整个产业的前进步伐己不可能再是每两年前进一个节点。

他们还对5nm及其之后的的选择做了考量。他们表示,在7nm之后,不确定性会明显提升。

10nm之后,IC设计上商和制造商的花费必然会急速上升,届时只会有少量的设计商和制造商有足够的金钱和资源能够跟上,业界之间的合作也势必会达到空前的高度。三星的相关负责人表示,他们的研发中心正在同时进行三个节点的研发,他们的最终目标是接近1.5nm。

在问到怎样实现的时候,三星负责人表示,他需要更强大的工具,材料和开放的创新,当然,三星并不能凭自己来实现相关事宜。

可能的选择

短期内,芯片制造商们明确地会在FinFet和二维的FD-SOI技术上将节点推进到10nm。到了7nm之后,沟道上的的“门”就会上去控制,这就亟待一种全新的晶体管架构。

7nm上的一个领先竞争者就是高电子迁移率的FinFet,也就是在沟道上使用III-V 材料的FinFet。III-V族 FinFET则可能会在PFET时采用锗(Ge)作为沟道材料,在NFET时采用InGaAs作为沟道材料。

锗无疑会是一个好选择。由于III-V族本身的特性,我们还需要在上面花费更多功夫。

实际上,III-V族材料已经受到了很多的关注,且可能会在5nm的时候推出。而在7nm的时候,锗和III-V族材料会是最有可能的竞争者。但是这些材料的窄能带隙也会给低漏电的晶体管带来麻烦。为此,对III-V族材料的期待从7nm迁移到5nm。但这并不排除近期会在源极和漏极上使用这种材料。

因此,由于III-V族 FinFET的可能延期,7nm还会采取什么样的方式去实现呢?IMEC考量了几个晶体管选择,得出了环绕栅极场效应晶体管、量子阱FinFET和SOI FinFET(应该是指UTB-SOI)三个答案。考虑到基本的CMOS器件遵从静电学,而环形栅极则是一种把栅极放置在沟道四面的结构。从某种意义上来看,在环形栅极的制程里,你需要从底部切断Fin。这样的话,在制作栅极到电介质时,沟道的下部会被填满。而现在这个位置只是纳米线,IMEC表示。

当然,SOI也是可取的,量子阱也是个不错的选择,你可以搭建一个有效的能量区域去关闭漏电通道。

关于7nm时候的沟道材料的选择,IMEC将其范围缩窄到两个:一个是由80%锗组成的PFET;一种是25%到50%混合锗的FET和0到25%混合锗且带有strain relaxed buffers(这里怎么翻译,应变弛豫缓冲层?)的NFET。最完美的选择材料是锗无疑。

硅器件的运行电压是0.8和0.75V,而锗器件的工作电压是0.5V,因此从静电学的角度看,你的确找到了你所需要的材料。毫无疑问,使用锗让你降低了Vdd,进而降低了功耗。

而在7nm之后,业界也给出了几种晶体管选择,如上面提到的环形栅极、量子阱、SOI FinFET,还有III-V族FinFET和垂直纳米线。IMEC表示他们正在考量垂直纳米线的方方面面。同时他们也在探索如何生长沟道,在集成方案的时候也在衡量是先使用沟道还是后使用沟通。

存在的挑战

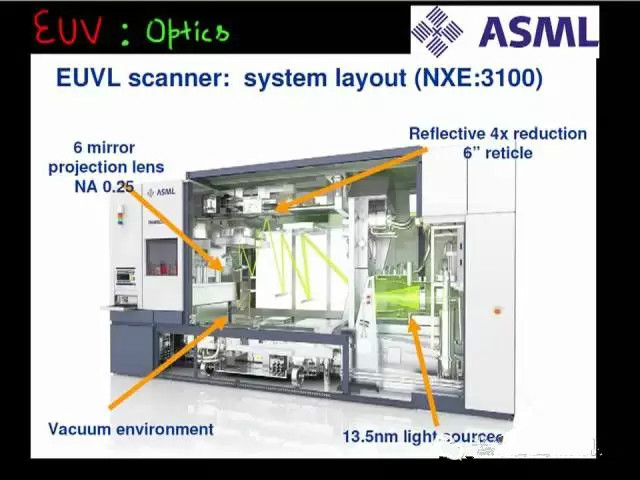

在10nm之后,半导体工业面临很大的挑战,首当其冲的是光刻技术。为了降低曝光的花费,IMEC的CMOS合作伙伴希望在7nm的时候用上EUV光刻。但由于电源功率多种原因的影响,EUV已经错过了很多个市场窗口,并且数次延期。根据媒体报道,截止今年八月:

半导体顾问公司的分析师RobertMaire认为EUV真能应用于量产应该是大约在2020年,在5nm时。近期TSMC公布它的计划也是在5nm节点。

Maire说英特尔可能会有不同的观点,它采用EUV设备在7nm,因为今年下半年它有可能进入10nm(Intel的10nm接近于代工厂的7nm,7nm接近于代工厂的5nm)。

因为现在16/14nm节点时通常采用两次图形曝光技术,如果EUV成功量产,可以避免在10nm及以下时要采用三次或者四次图形曝光技术,成本上可大幅的节省(原则上应该是由于EUV分辨率高,不需要拆分Mask成为几张子Mask,从而节省了Mask成本,同时节省了制造时间)。

从20nm节点开始要采用两次图形曝光技术,芯片制造商人为的把工艺节点分成两类,如20nm及10nm都是过渡节点,相对工艺寿命短,而28nm,16/14nm及7nm可能是长寿命节点。

ASML的市场部总监Micheal Lercel说EUV系统量产需要安装250瓦光源,保证每小时125片,而现在的光源是125瓦,只能每小时85片,ASML正在实验室中研发210瓦光源。

目前大于200瓦的EUV光源有两家供应商,分别是ASML的Cymer及Gigaphoton。两家供应商都认为未来500瓦光源有可能性。

目前用于EUV掩膜保护的Pellicle只能承受125瓦的热负荷,离开250瓦的目标尚有一段距离。

由于EUV光刻胶它的工作模式是采用反射的二次电子,不同于通常的193nm光刻胶,因此尚需要突破。

目前EUV光刻的成本非常接近于三次图形曝光技术。

ASML希望它的EUV系统能有大於90%的uptime,但是目前在4周工作周期中它的uptine大於80%。而ASML计划2018年时它的EUV设备的产能再扩大一倍达到年产24台,每台售价约1亿美元,目前芯片制造商己经安装了8台,正在作各种测试。(uptime不懂)

设备从研发到量产有很大的差别。光源系统的可靠性要求十分高,即便系统工作在真空环境下要求每秒能击中50,000次融化的锡珠(这句话读不懂。。。。)。因此新的光源体积很大,相比之前的准分子激光源更为复杂,它的尺寸如同电冰箱一样大,工作在洁净厂房中。

业界都希望在7nm的时候有EUV和多重曝光加持。并将图层的pitch降到21nm,这其实比EUV本身能够分辨的最小pitch还低,要将如Fin等的图层做到21nm,那就需要EUV加上双重曝光去实现。毫无疑问,在未来,业界会将推动这些技术的全部全方位发展。

如果EUV折戟,那么业界就会将目光转向193nm沉浸和多重曝光。有业界人士表示,如果EUV没准备好,那么Fin就会使用spacer patterning(侧墙转移技术)。我们也很清楚的知道,spacer patterning需要沉积和刻蚀,如果你想重复这个过程,那么你就需要经过两次浸没式光刻,但这样做的话,成本会显著提升。有时候你还需要做第三次,这样的话成本就更高了。

Patterning只是众多难点中的一个,到了7nm之后,你就有了22nm, 14/16nm, 和10nm FinFET,那就是拥有了三代的FinFET 技术。随着你缩小FinFET的尺寸,你会在沟道的栅极耦合上面临与平面型器件相同的问题。

因此到了7nm,业界需要寻求一种能降低栅极长度和维持高性能的新晶体管技术。应用材料晶体管技术部门的高级总监Brand认为环形栅极场效应管是最有效的选择。他表示未来

他将押重注在环形栅极场效应管上。

Brand指出,环形栅极场效应管并没有想象中那么不稳定,它其实非常实用,你甚至可以把它当做FinFET的改良版。实际上它只是在沟道上增加了几个面。Brand不确定环形栅极场效应管是否能在7nm实现,或者在5nm实现,这一切都取决于业界的进展。更决定于公司在降低栅极长度上是否足够激进。

环形栅极场效应管需要复杂的纳米线架构,但这个在精度控制上面并没有验证。这中间还会面临很多挑战,其中一个就是接触电阻。

至于花费方面,从Intel的22nm开始,和传统的Planar相比,在工艺流程中使用FinFET需要额外付5%的费用,因此在工艺制程中你可以轻易引进一些“破坏性”的新技术。如果是用环形栅极场效应管做水平图层,很多步骤都是和以前相同。当然,也会添加一些类似epi(外延)、selective removal(选择性刻蚀or选择性去除) 和 ALD等工序。

如果几十年后,业界用平面晶体管设计和生产芯片,这又是另一个课题。目前看来,IC设计和制造群体必须拥抱FinFET。在7nm的时候,晶体管势必会带来翻天覆地的变化,届时相关的设计也会被革新。

正是基于这个原因,有些人坚信业界应该扩展FinFET。环形栅极和其他架构也会拥抱晶体管的变化,做出相应的转变。从平面晶体管到FinFET的转变,设计和制程发生了重大的改变。因此除非是强烈需求,否则业界应该不会轻易切换到其他其他架构。

10nm之后,也会有很多方式去扩展FinFET,例如从Fin过渡到三五族、锗,或者将Fin延伸,作为FinFET技术的自然扩充。但这项技术的因素并没全部搞定(翻译带商榷)。例如关于三五族半导体,我们还多东西需要去探索,但我们最终肯定能够到达“终点”。但我们是否会在7nm实现,那就不一定了。

毫无疑问,芯片行业正在全速迈向7nm和5nm,TSMC也展望在2018年推出7nm芯片。台积电和其他业者也在跟进环形栅极晶体管的研究,但并没有什么是一成不变的,因为如果下错注了,损失会非常惨重。因此台积电表示会衡量所有的方式。

从目前的情况看来,硅基的FinFET会在10nm的时候后继乏力,因此行业都在探索新型的晶体管架构(前文有提到)。

另外有一点需要注意的是,7nm和5nm,BEOL是在衬底上增加物质(增加材料 这样翻译是否更合适?),通过叠加金属和钝化层来完成互联功能)对于延续摩尔定律会产生很重要的作用,而实际上,BEOL是远远落后于晶体管制造前端和中端的工艺,它会随着节点的演进导致RC延迟呈现指数级增长。应用材料的专家表示,我们未来会在头发那么点的宽度里填充超过1000个内部连接。因此在未来我希望从我们的终端客户那里了解到他们对于后段材料的需求。因为他们普遍反映后段工艺的节奏没跟上。

业界正在寻找新的方法,希望在10nm的时候降低RC延迟。至于7nm节点,从业者正在探索新的工具和材料突破。行内人都认为到7nm的时候,市场是完全开放的,并没有什么是必然的。

行业也在寻求新的材料去改变传统的架构,如Co、Mn和Ru,除了材料以外,业界也在其他方面探求解决办法,例如碳纳米管、石墨烯。业界人员也应该跳出这种固有思维,因为除了材料之外,还有很多其他问题亟待解决,例如为了避免RC延迟,芯片制造商需要追求解决办法,例如2.5D和3D芯片,垂直纳米线等等。

光刻和材料问题

在一个设备中,有两种类型的BEOL连接线,一种是intermediate,一种是global。intermediate解决设备中低级别的连接问题。而和以往一样,RC延迟的问题是与连接 intermediate层的global 线相关的。从20nm开始,芯片制造商在制造芯片过程中增加了另外一种线,加大了芯片的复杂性。那就是MOL(middle-of-the-line),(我了解的是MOEL,请按原文,应该是增加了middle end of the line,MEOL,或者就是前文的MOL,MEOL引入了Local Connect,增加区部互联性) 这就在设计中增加了区域互联(这里应该是就是前面的Local Connect)。

在BEOL那个阶段,有非常多的步骤,但主要可以分成两个类别,那就是patterning 和 dual damascene。最初,在整个流程里面,芯片架构的每个层级必须曝光布线图。为此,芯片制造商在FEOL(FEOL完成的是器硅片上器件结构的过程,比如做栅,做源漏,这个过程对设备的要求是很高的,对洁净度的要求也很高)和BEOL使用193nm沉浸和多层曝光。

BEOL的布线在每个节点的花费是很大的,并且极具争议性的。其中金属层和连接层的争议是最大的。如果用193nm沉浸去实现,就有点艰难,这就为什么对EUV有极大的需求(后段工艺的前几层是工艺中对光刻要求最高的几层,最高精度的几层需要拆分mask)。

7nm之后,业界都选择EUV为后段的pattern,EUV会把BEOL带回到单次曝光的年代,如果EUV的产量能够达到每小时150片晶圆,BEOL的成本将会降低30%。但就目前看来,EUV的进度没跟上。如果EUV真的错过了7nm,芯片制造商必须去寻找新的光刻解决方案。

EUV光刻的缺席会带来更多的连线层需求,这无疑就增加了成本。

而内部连接,现在也面临各种挑战,例如高电流密度,这会给芯片设计和生产带来影响。

随着节点的演进,人们探讨过很多材料,例如在65nm的时候,人们就研究了钌,相对于钴而言,它有很好的性能,能充当重要的角色。另外由于钌能够使铜回流,因此你可以想想一下利用PVD来满足内部连接。

钌当然也是有缺点的,例如很难抛光,对于制造来说,钌是非常不友好的。

其他的选择

半导体业界一直在探讨各种解决办法,但经常会碰到失败或者昂贵的问题。例如业界曾经为7nm探讨过SAV(self-aligned via)规划,这个能够解决在紧密pitch情况下的via-to-metal短路问题,但SAV有着对不准的大挑战(对光刻的套准精度要求极高)。

业界也在探讨碳纳米管和石墨烯在5nm时候的功效。从工艺流程上看,碳纳米管是利用CVD生长的。然后在平坦化制程期间,会用到一种混合物封装去保护其架构。

而在5nm,IMEC也开发了一种垂直纳米线晶体管,它能够使用常用材料或者碳纳米管实现内部连接。其实在5nm或者以后,除了垂直,我相信行业没有其他方法可选。

除了垂直纳米线,我们还有其他技术可供候选,那就是三维芯片。其中包括了在每个三维芯片上加上堆栈、对其和连接尖端晶体管。在最小配线幅度下,monolithic 3D 芯片能够提供的连接是2.5D/3D TSV的一千倍。

CEA-Leti,作为这个技术的主要推动者,指出了三维芯片的挑战,那就是顶部的晶体管热平衡需要被限制在一定范围去保护底部的FET。换句话说,那就是业界必须找出600摄氏度下的电子活化技术。于是CEA-Leti去研究了包括激光退火工具。这个工具只有308nm的波长,且还有短脉冲。

初次之外,还有很多传统的方法,例如堆叠芯片。平面型期间的电阻系数问题会加速使用TSV技术开发2.5D和3D芯片。